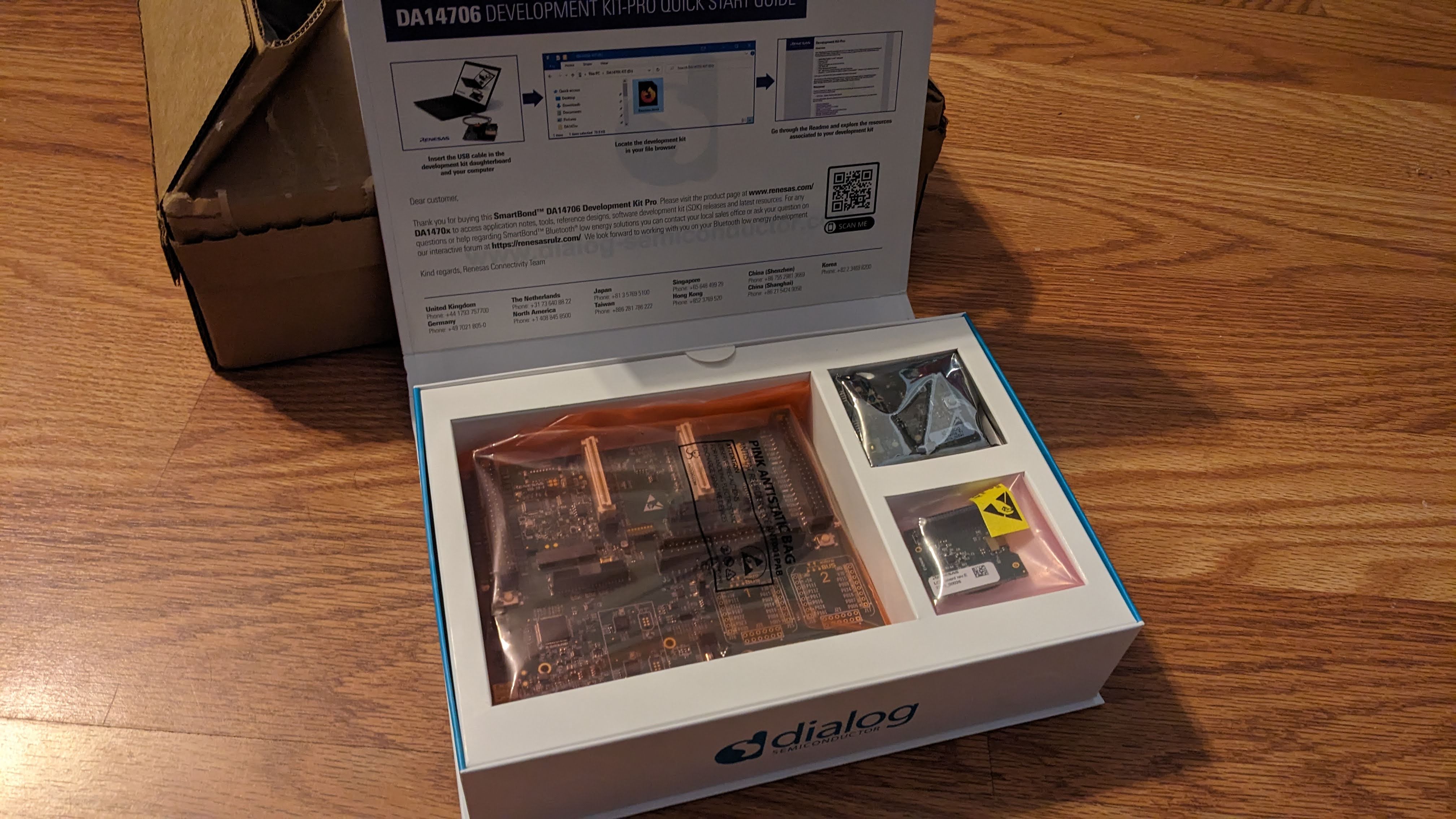

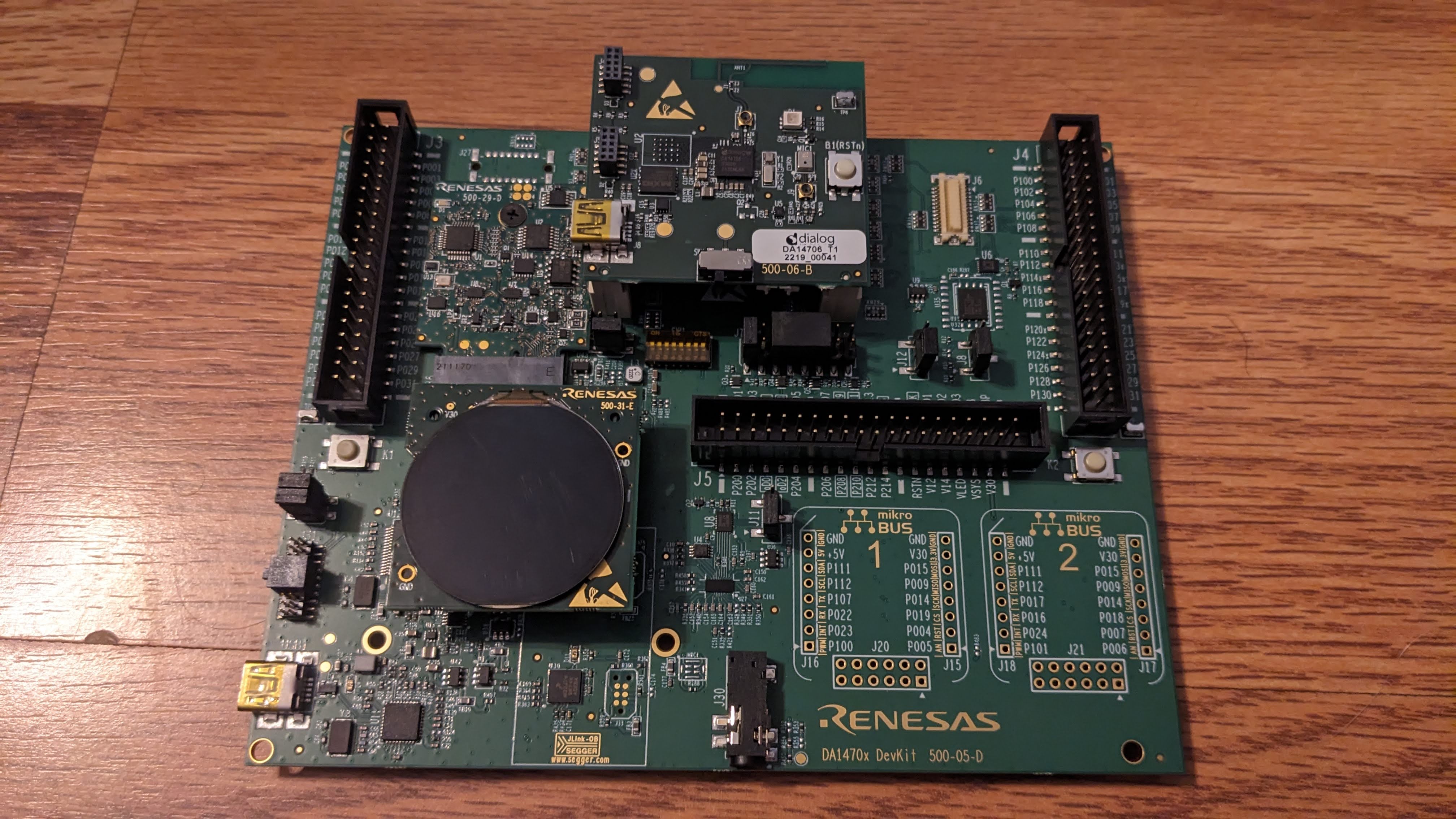

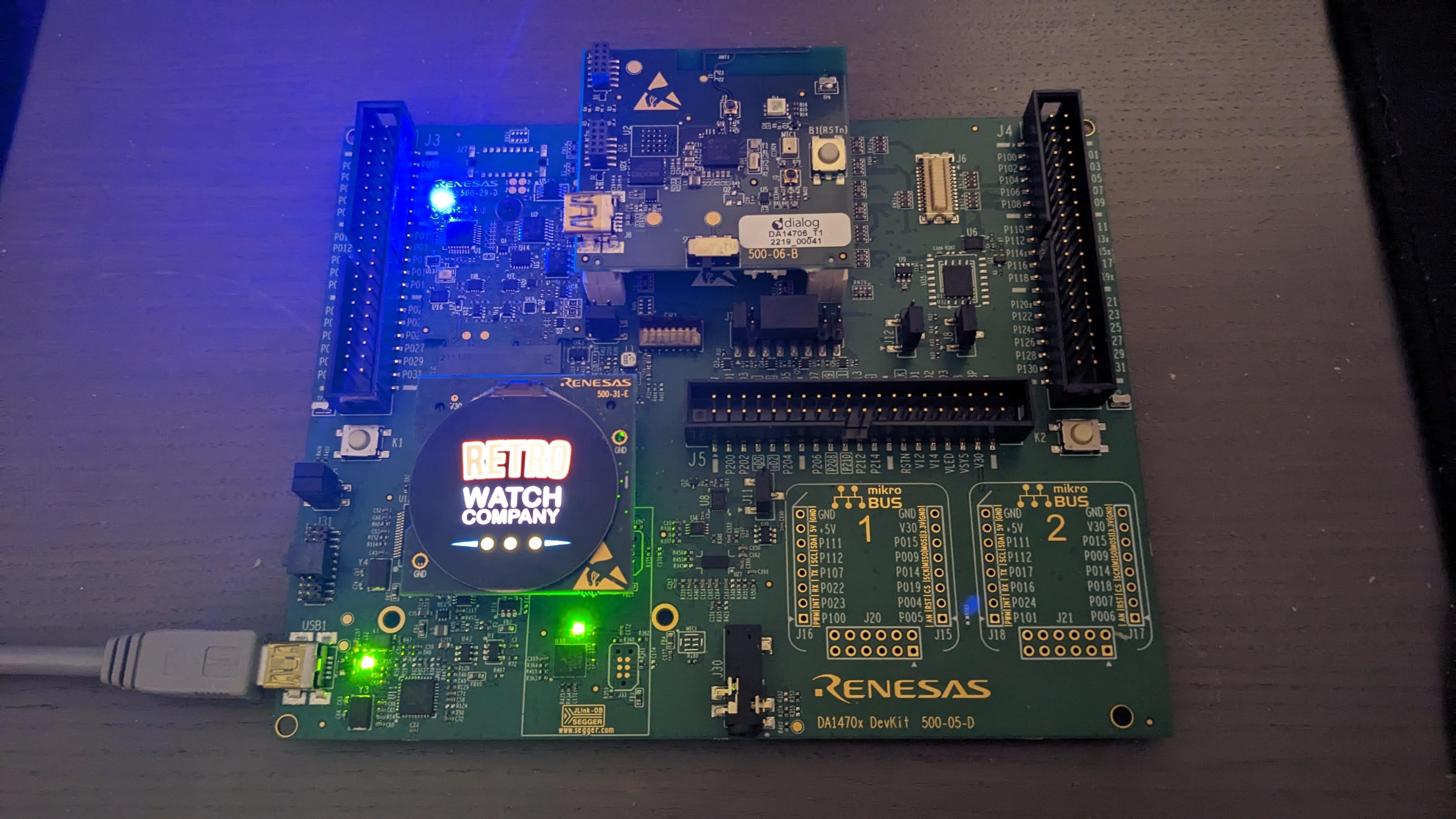

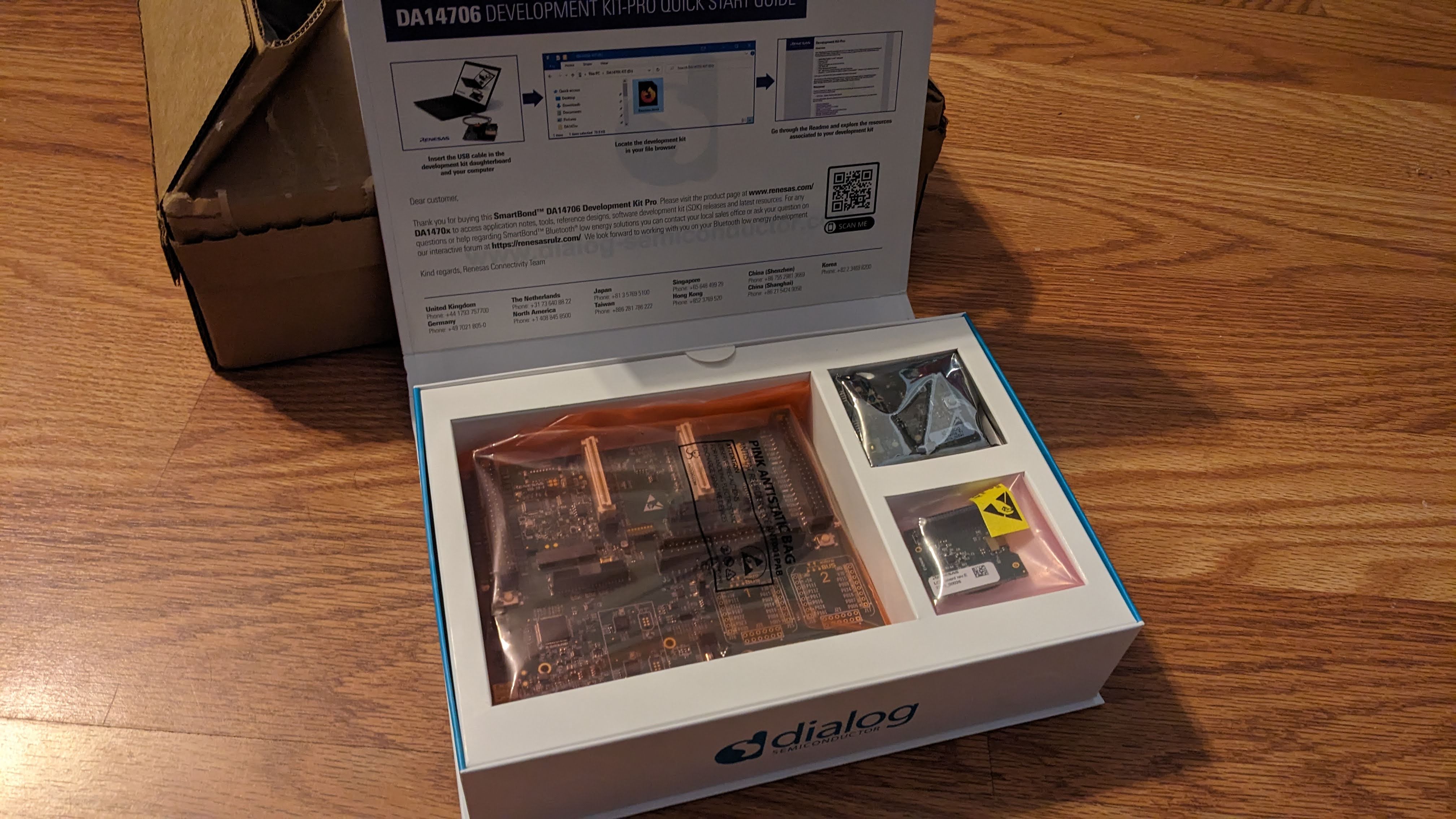

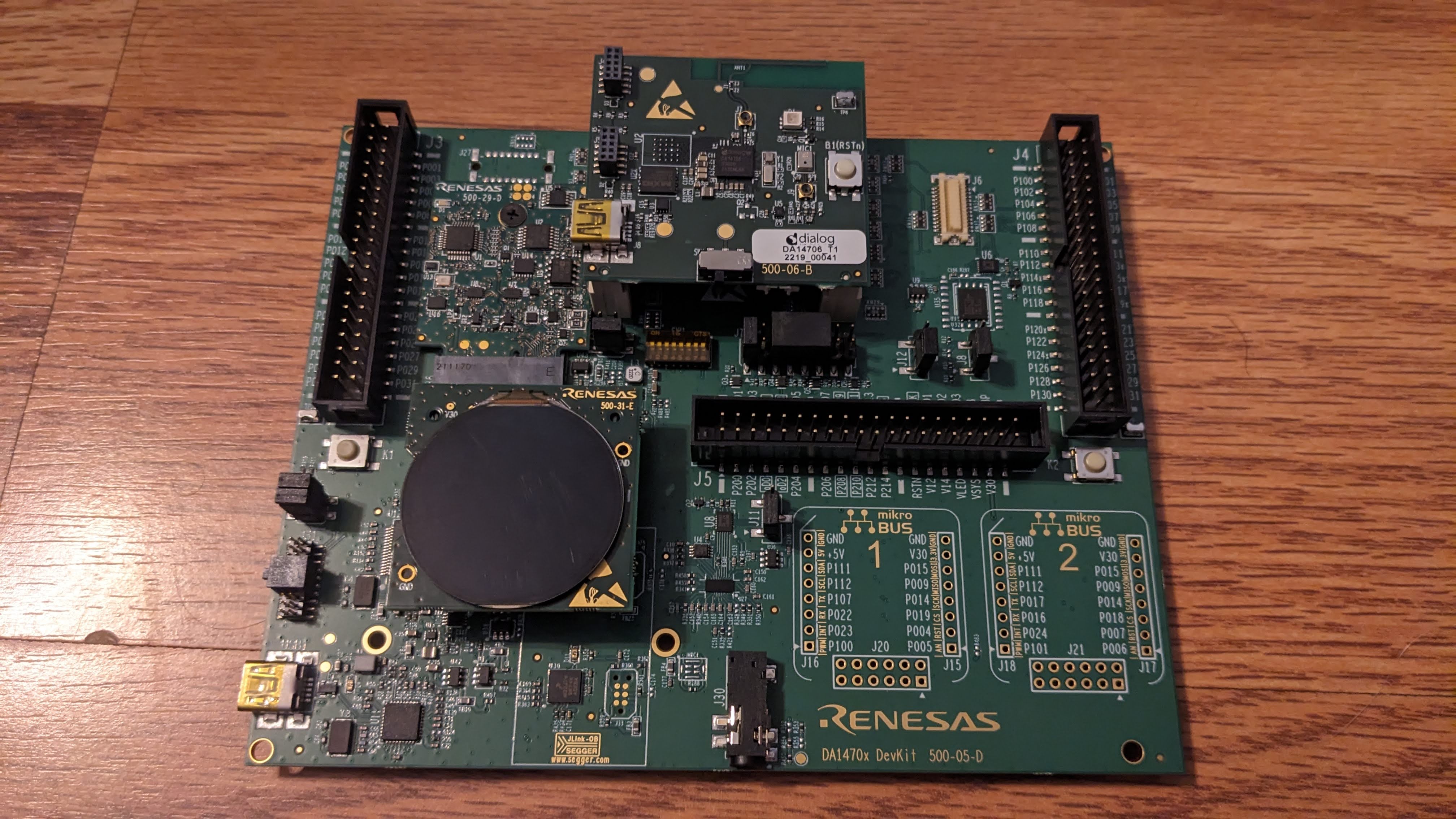

Look what arrived in the mail today! It's a Renesas DA14706-00HZDEVKT-P. Thanks @Dovoto for gifting me this magnificent piece of kit!

Look what arrived in the mail today! It's a Renesas DA14706-00HZDEVKT-P. Thanks @Dovoto for gifting me this magnificent piece of kit!

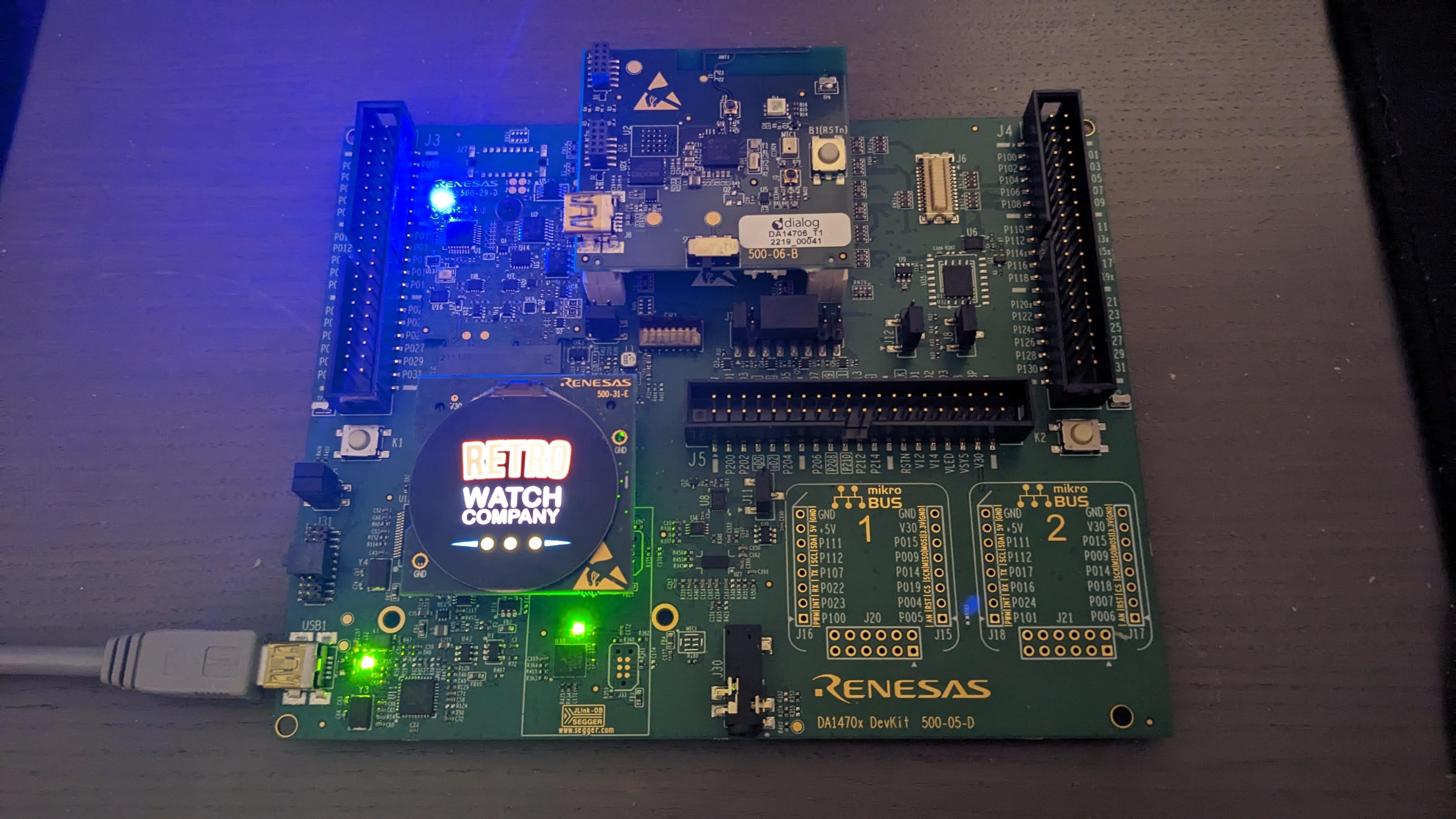

My little pretties!

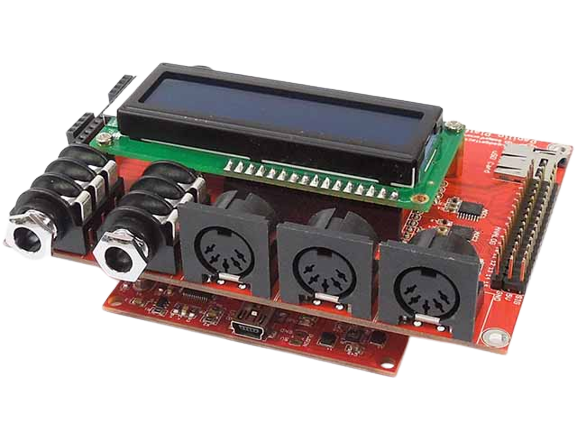

I received my YM2149 Synth from Catskull Electronics a few days ago! Thanks to David for the cool extras included 🙂

Having lots of fun with it! I've modified David's fork on Github to enable it to play back YM files over serial. It uses a C# app to parse the YM file and stream it over USB with the Teensy in Serial mode.

Cool thing is there are lots of cool songs in YM format that you can play. My musician friend SpaceFractal uses Vortex Tracker to make tunes and it can export to YM format for playback on the YM2149 Synth!

UPDATE: You can download YMPlayer from here

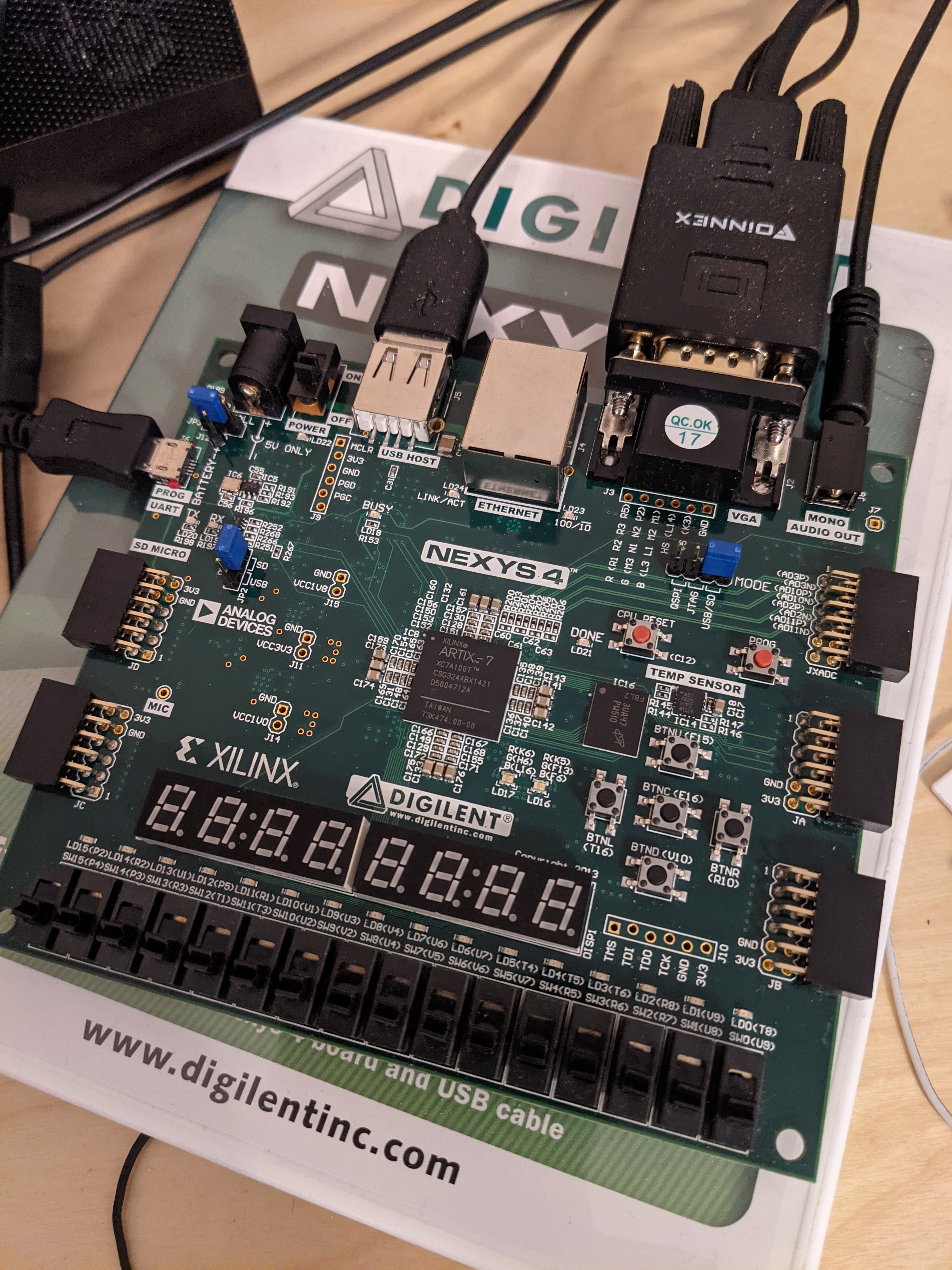

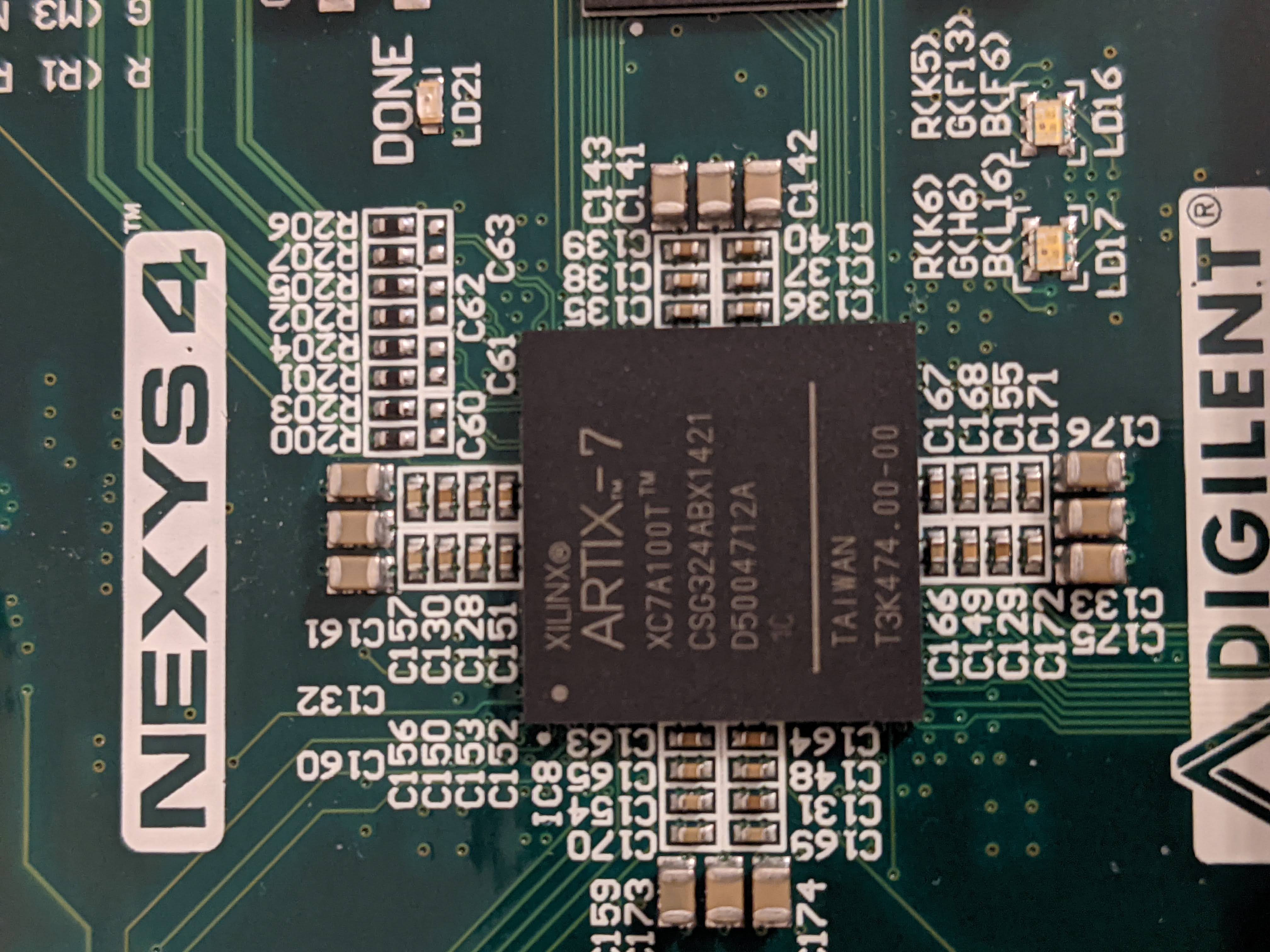

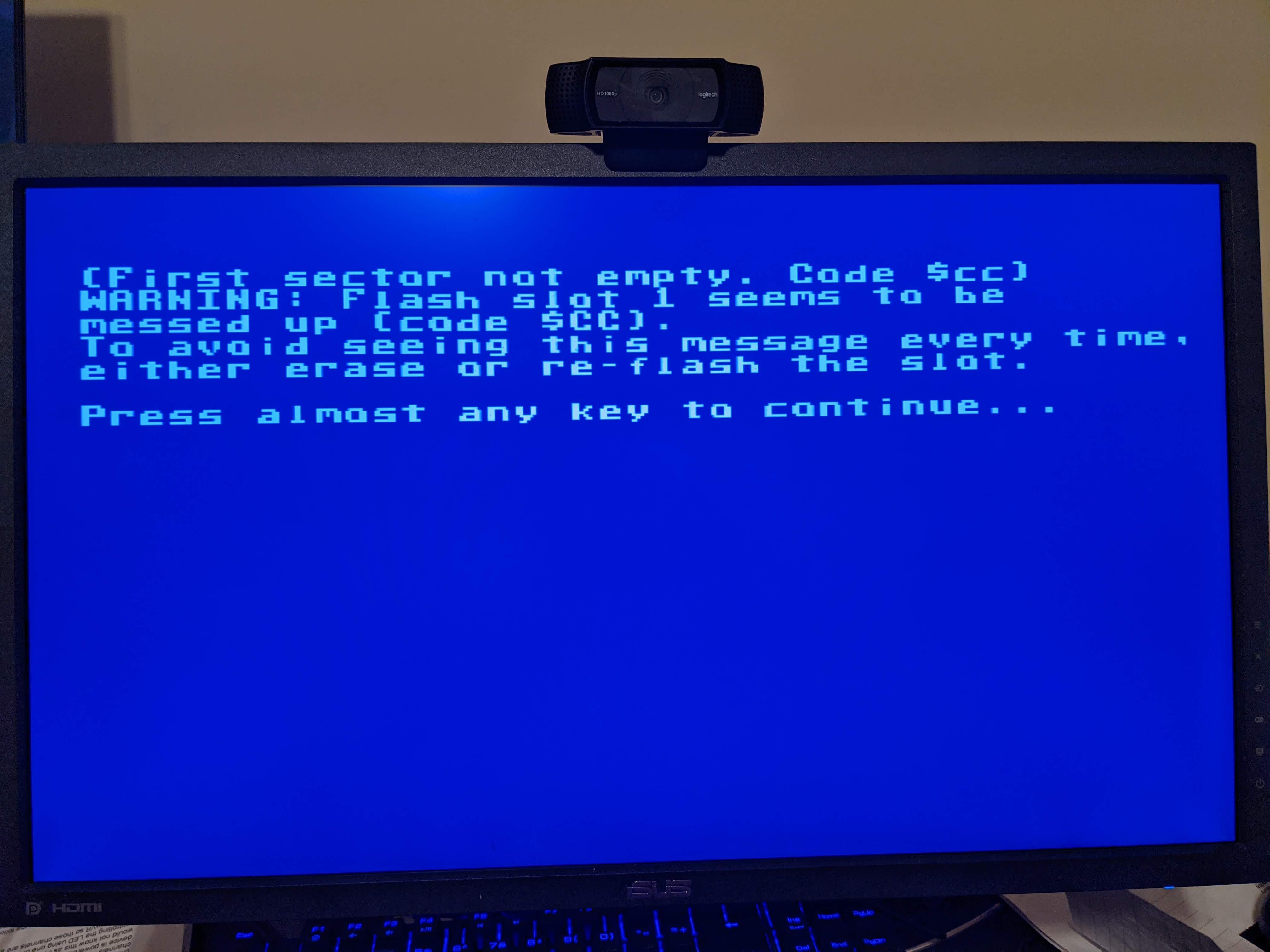

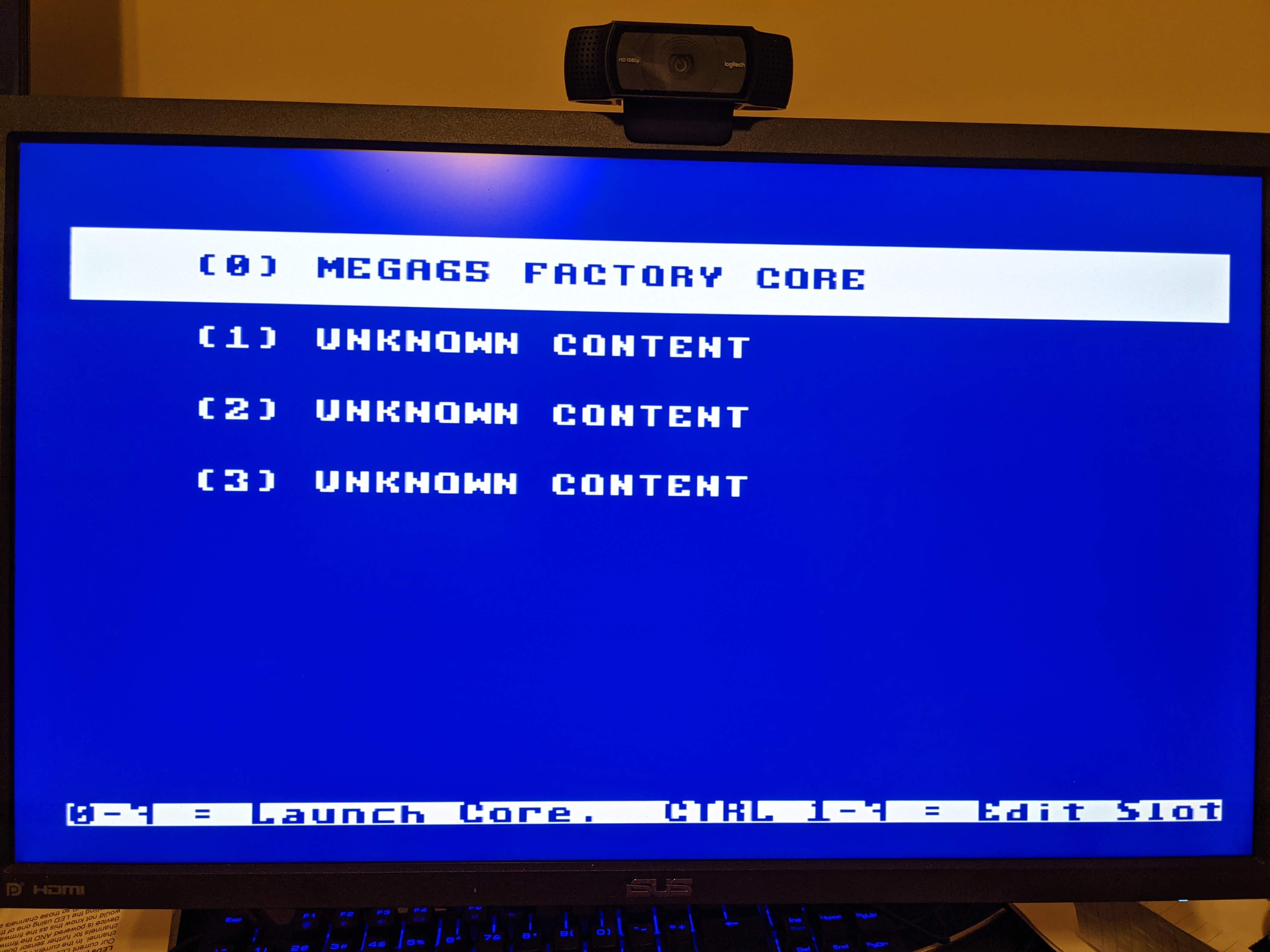

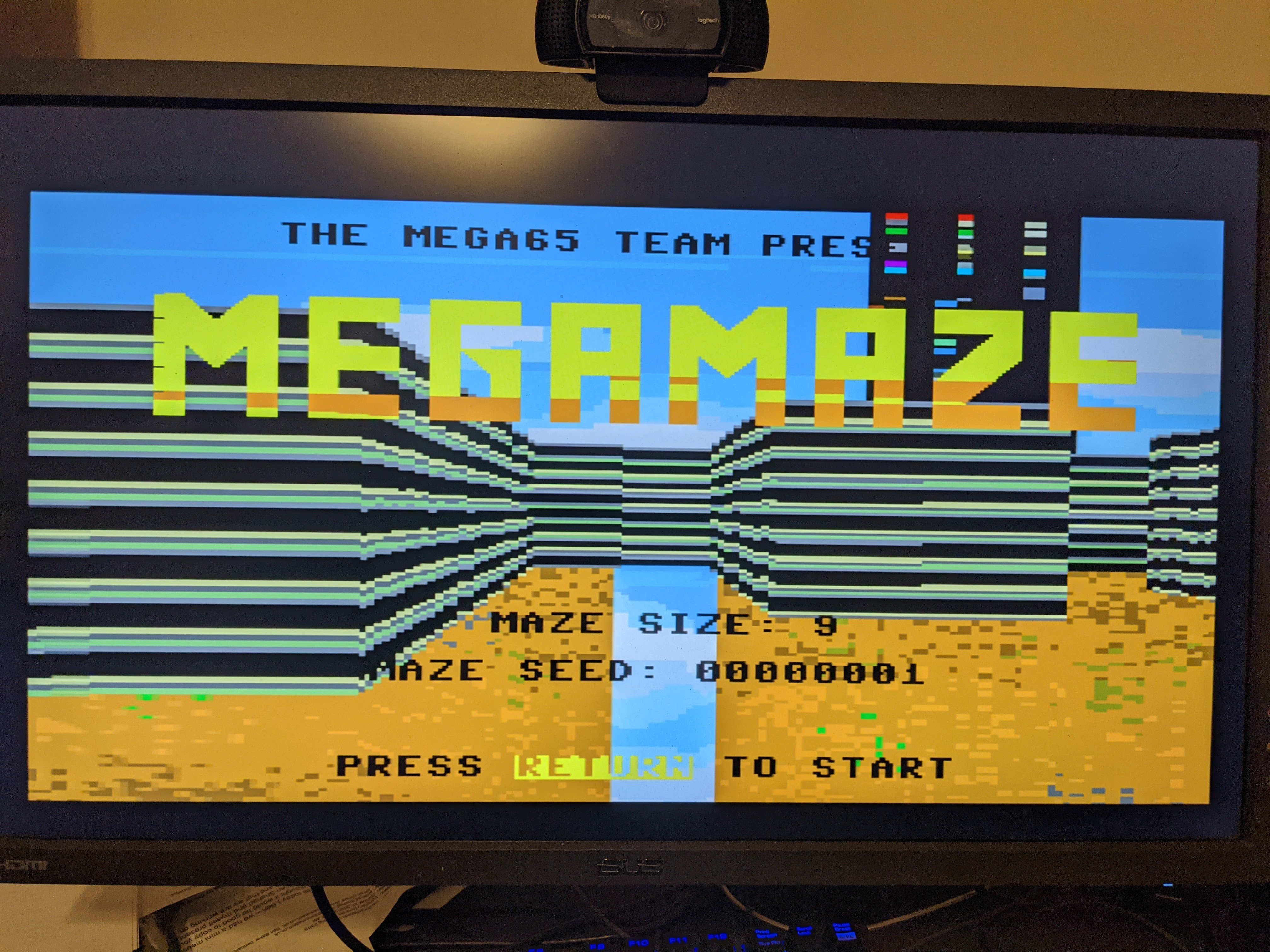

I recently bought a Nexys 4 Artix 7 (PSRAM not DDR version) and I'm trying to program the memory device so it boots directly into MEGA65.

I've compiled the latest nexys4.bit and nexys4.mcs files using Vivado 2019.2. Programming the memory device appears to be successful until I do a "Boot from configuration memory device" and then "Refresh Device". It shows a BIT05_0_CRC_ERROR. JP1 is set to QSPI.

So it looks like it's just the ConfigRate setting that needs changing. 33 MHz is too fast so the next lowest setting 26 MHz appears to work okay.

set_property BITSTREAM.CONFIG.CONFIGRATE 26 [current_design]

Now the only remaining issues are clearing and writing to flash from the MEGA65 configuration and having support for PSRAM again so things ike the MEGAMAZE demo have enough extended RAM for textures.

This little beauty arrived today!

I made some updates to the NetSID project. You can download the full ISE project from https://baker76.com/download/fpga/netsid.zip

There are now two ISE project files NetSID_pipistrello.xise and NetSID_papilio.xise which have the appropriate ucf and clock files. These support the Pipistrello and Papilio FPGA development boards respectively.

Here is a list of the main changes:

Eg.

using COM15

listening on port 6581

connected

sid count: 3

[0] model: 0

[0] position: 206

[1] model: 0

[1] position: 50

[2] model: 0

[2] position: 206

[0] resampling method: low quality

[0] clock source speed: PAL

[0] clock source speed: PAL

[0] clock source speed: PAL

sid count: 3

[0] model: 0

[0] position: 206

[1] model: 0

[1] position: 50

[2] model: 0

[2] position: 206

[0] resampling method: low quality

[0] clock source speed: PAL

FPGA requested pause, buffer full...

[2] 39346 Bytes/s, block size: 288

FPGA requested pause, buffer full...

[0] 30406 Bytes/s, block size: 316

FPGA requested pause, buffer full...

[2] 29653 Bytes/s, block size: 332

FPGA requested pause, buffer full...

[2] 30620 Bytes/s, block size: 300

FPGA requested pause, buffer full...

[0] 30347 Bytes/s, block size: 316

FPGA requested pause, buffer full...

[1] 30633 Bytes/s, block size: 316

FPGA requested pause, buffer full...

[2] 29623 Bytes/s, block size: 332

FPGA requested pause, buffer full...UPDATE: This project is now hosted on GitHub here

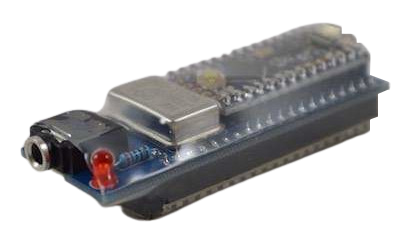

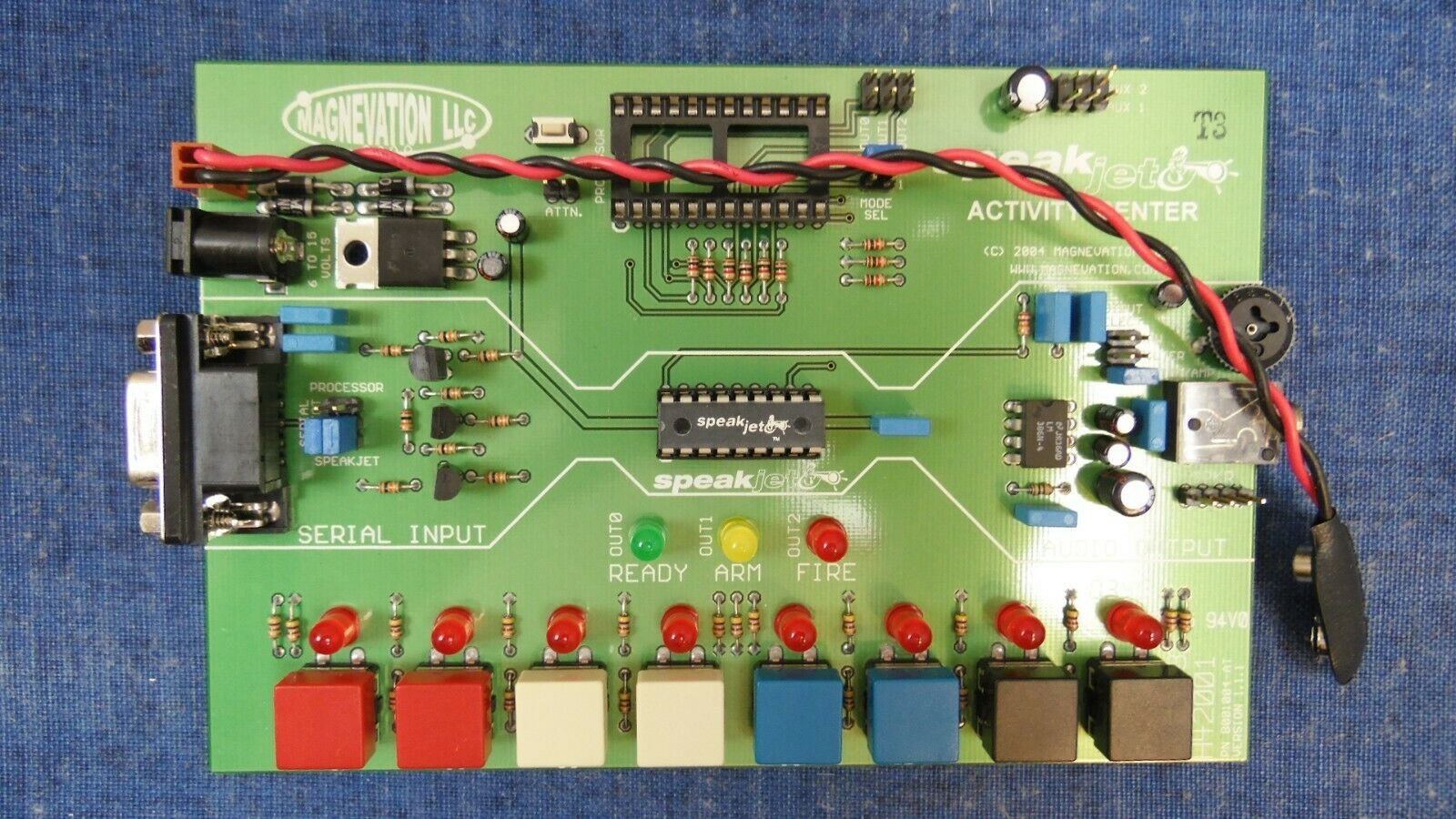

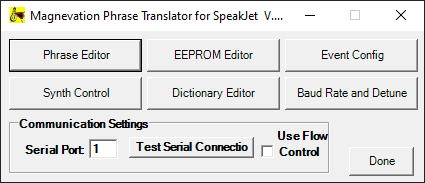

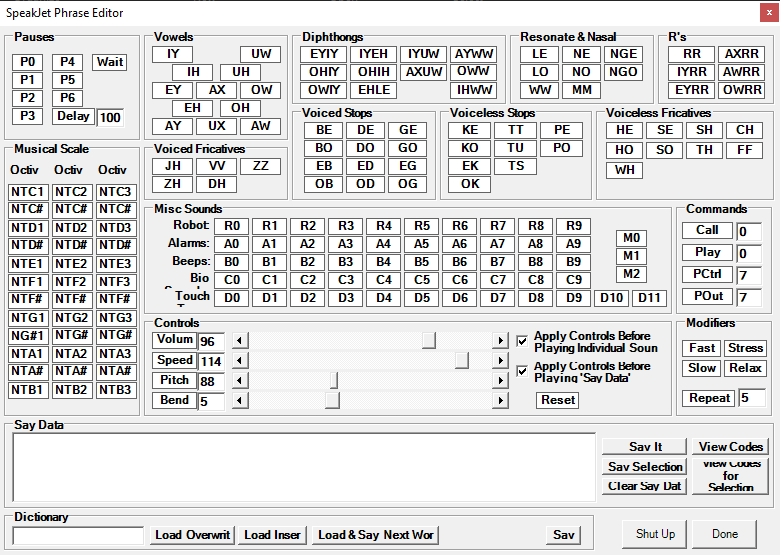

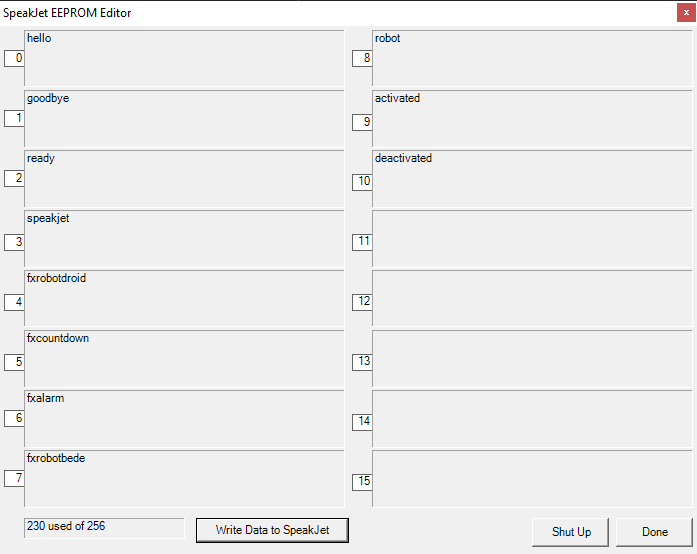

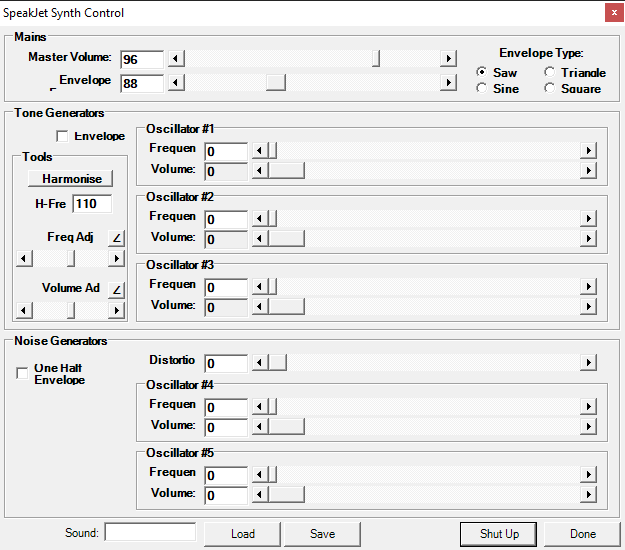

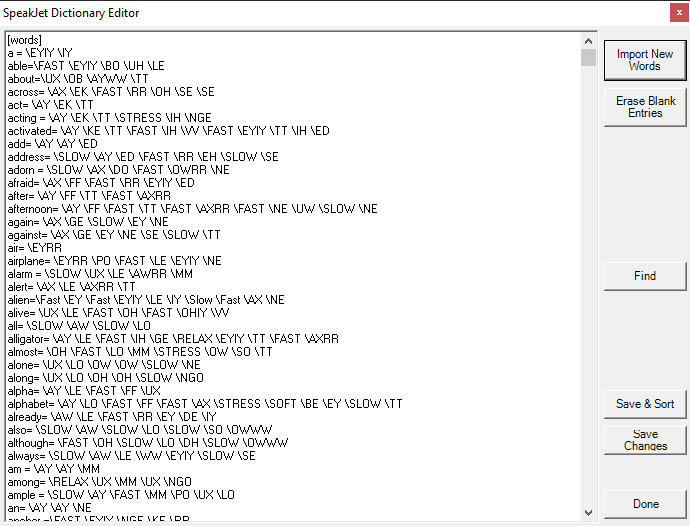

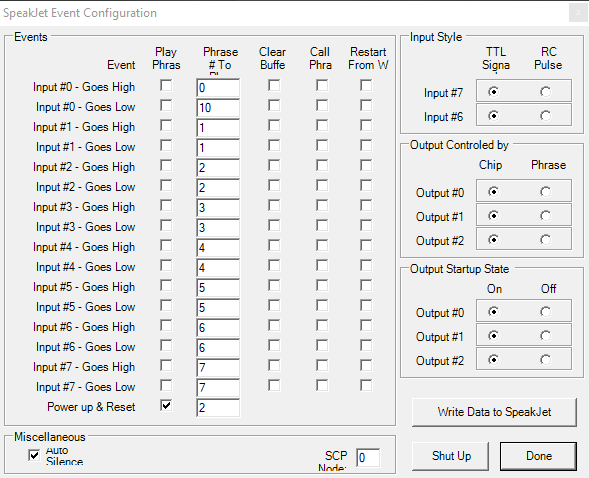

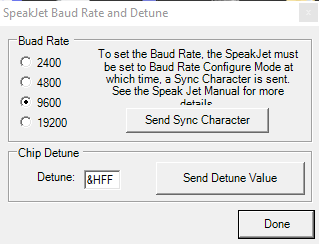

I scored one of these on eBay for $20 and have been playing around a bit and discovered it's the same chip used in the AtariVox+ Speech Synthesizer.

I decided to port the PhraseALator application to C#. Part of the process was to change from Mscomm32.ocx to .NET's SerialPort class in the System.IO.Ports namespace.

I made a C# source to PhraseALator available on Github here.

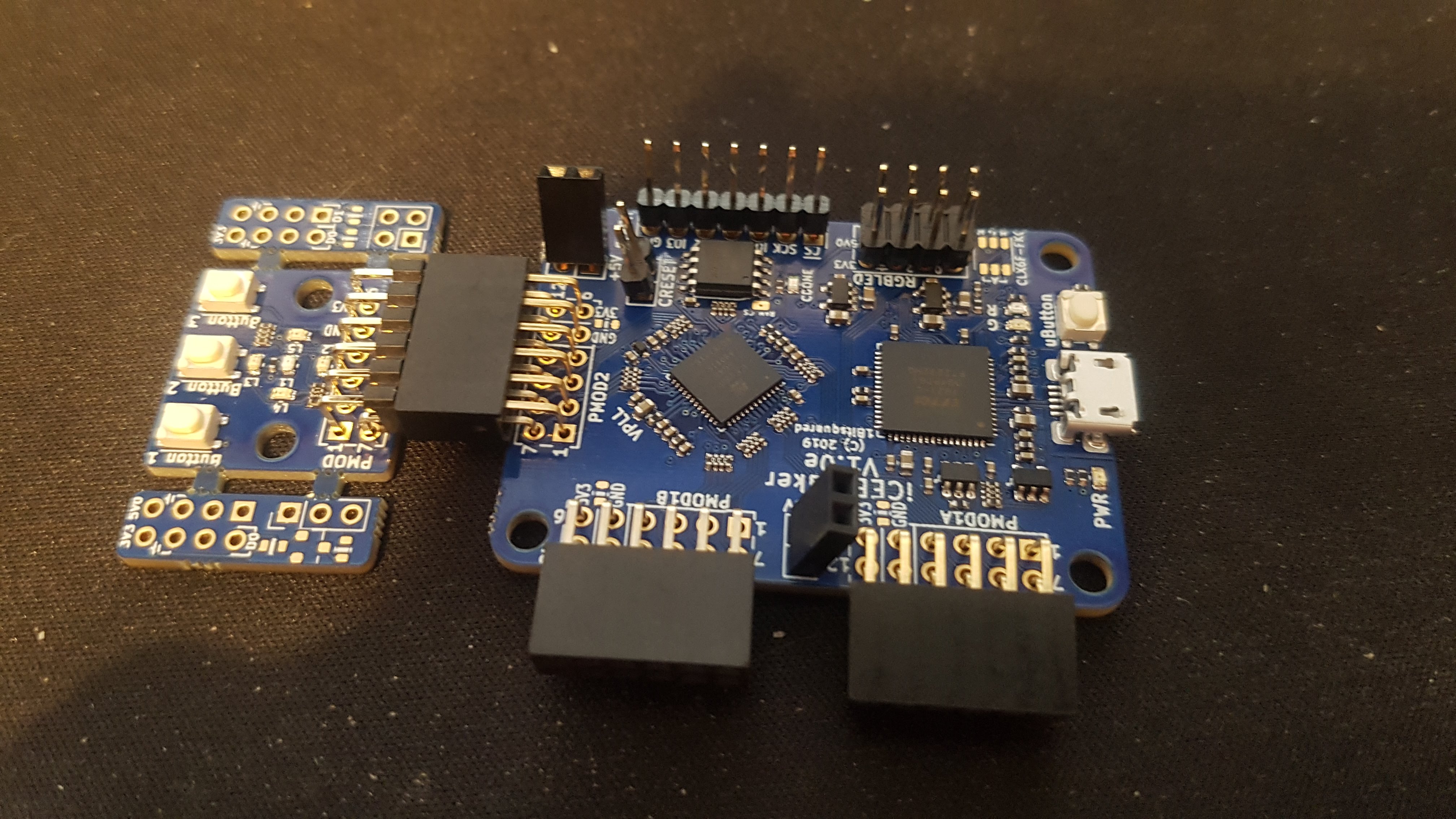

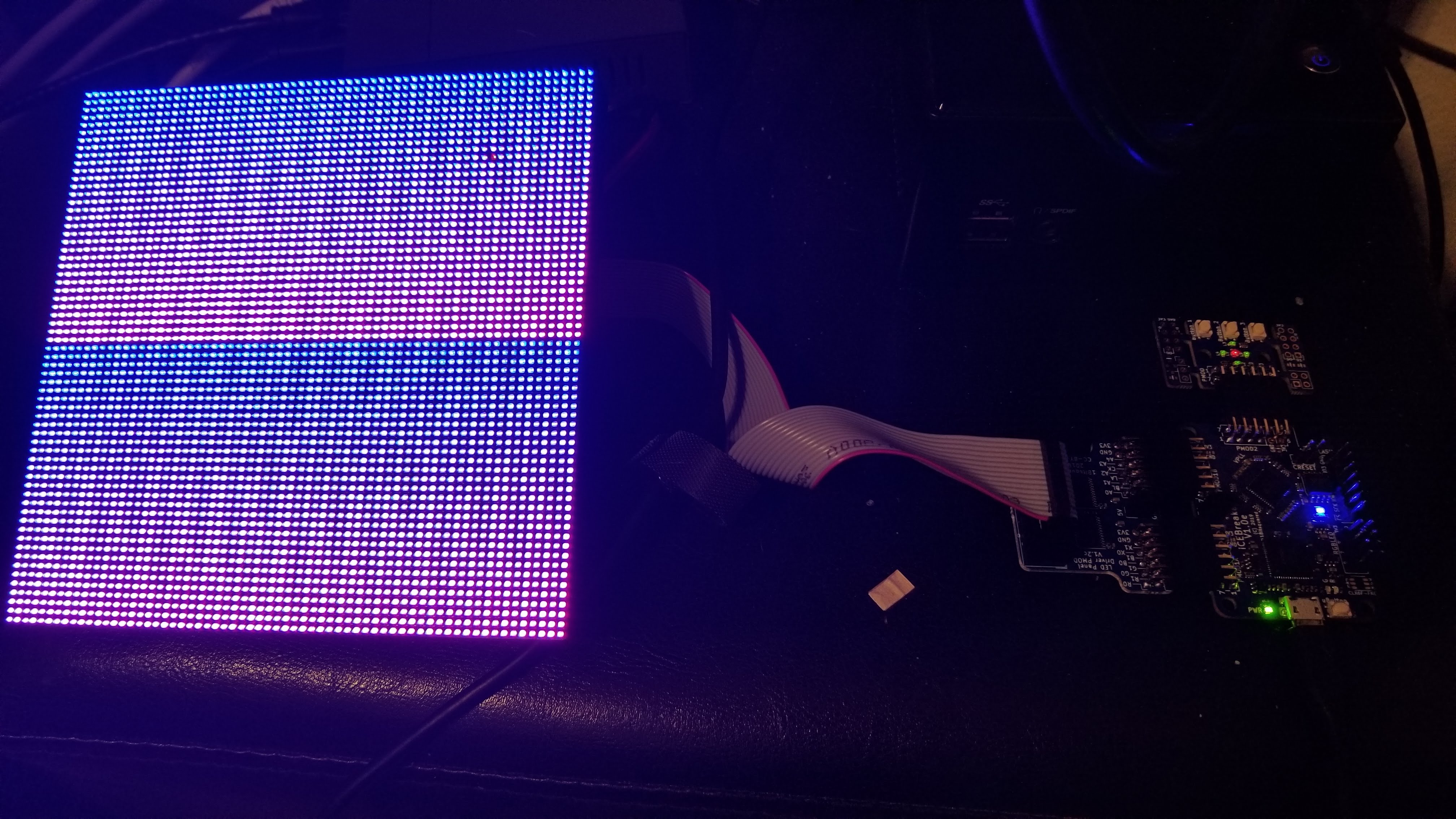

I'm playing around with my iCEBreaker FPGA today. Got output to an RGB Matrix using the LED panel driver Pmod.

I have a project in which I want to create a console in FPGA and was disappointed to find the Papillo project was pretty much dead and did not support the Xliinx 7 series. I found the Bonfire RISC-V (RV32IM) processor and decided this would be a great replacement for the ZPUino.

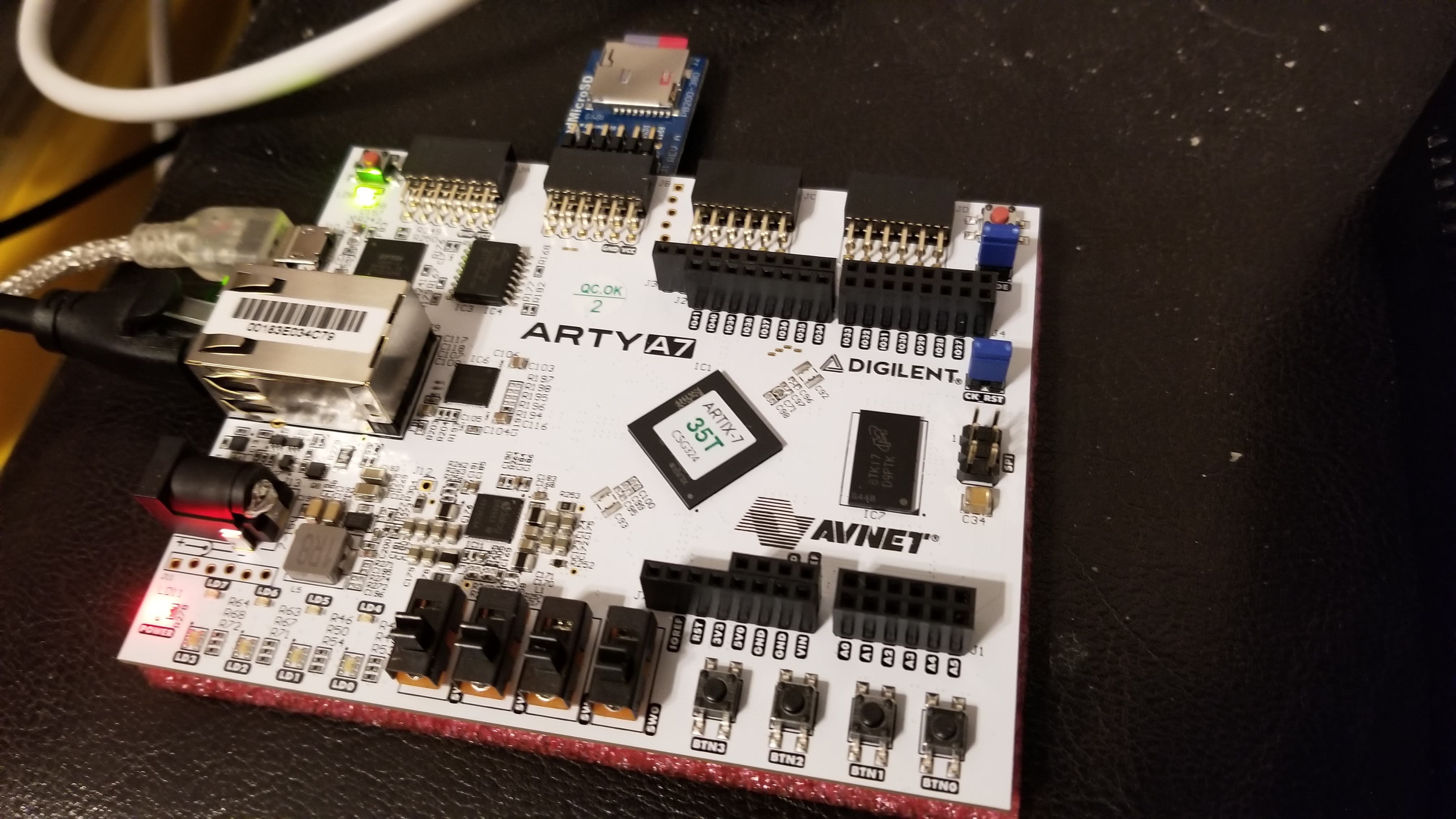

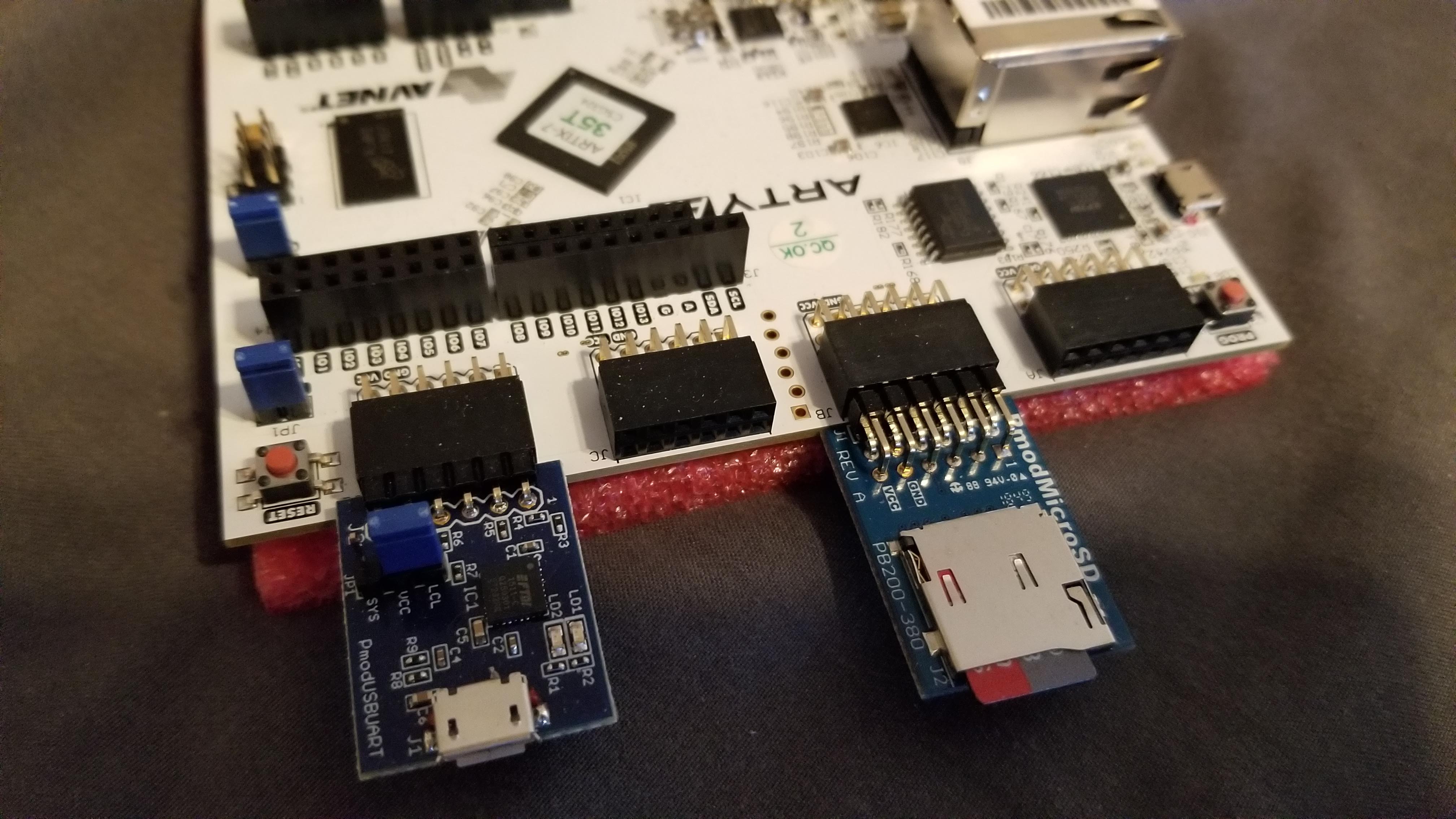

I recently purchased an Arty A7-35T board so I can run the Bonfire processor. I plugged in a Micro SD and USBUART Pmod. The Micro SD slot is for storing and running Lua applications and the USBUART Pmod is for debugging (more on that in another post).

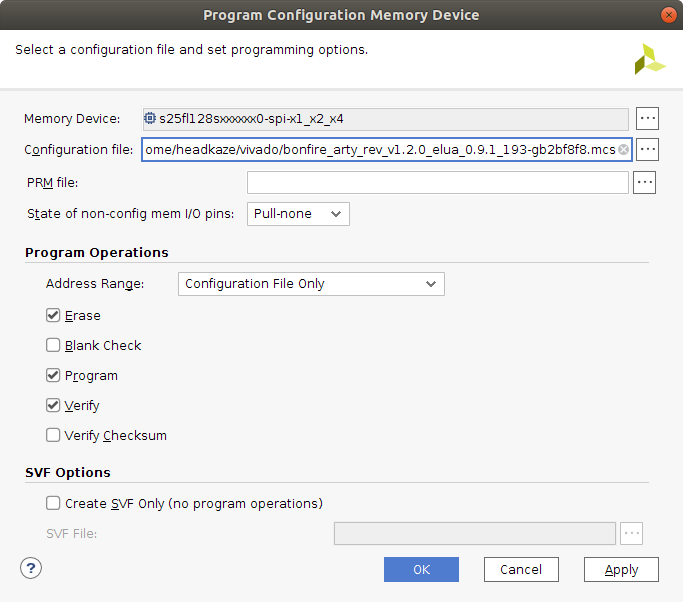

I successfully flashed the bonfire_arty_rev_v1.2.0_elua_0.9.1_193-gb2bf8f8.mcs image.

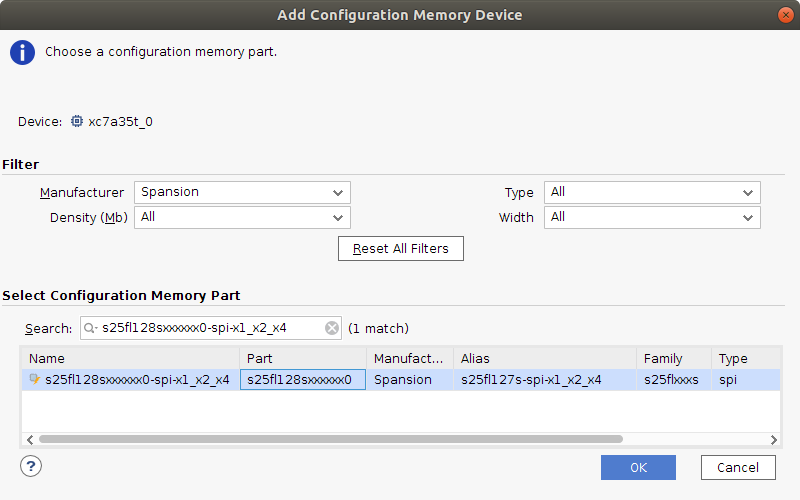

The first issue I came across is the Configuration Memory Device is different on my board. Mine has a Spansion s25fl128sxxxxxx0-spi-x1_x2_x4 not a Micron mt25ql128-spi-x1_x2_x4.

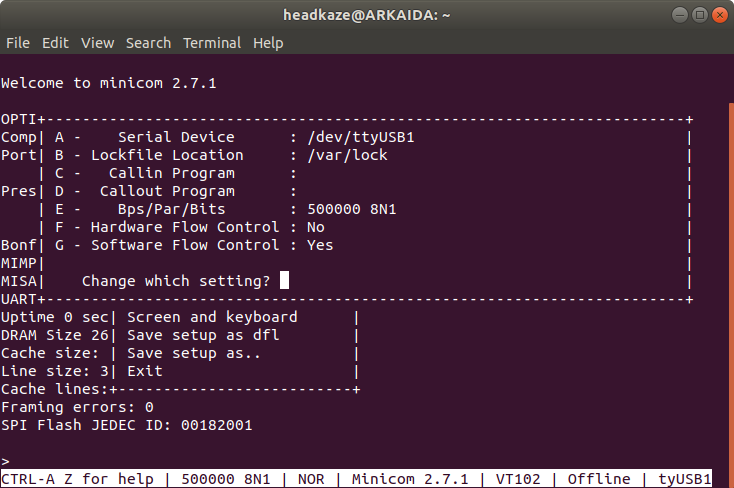

The second issue I had was using minicom. I could not get any response from the board until I did the following:

So now I have successfully connected to my Arty running Bonfire processor! 😄